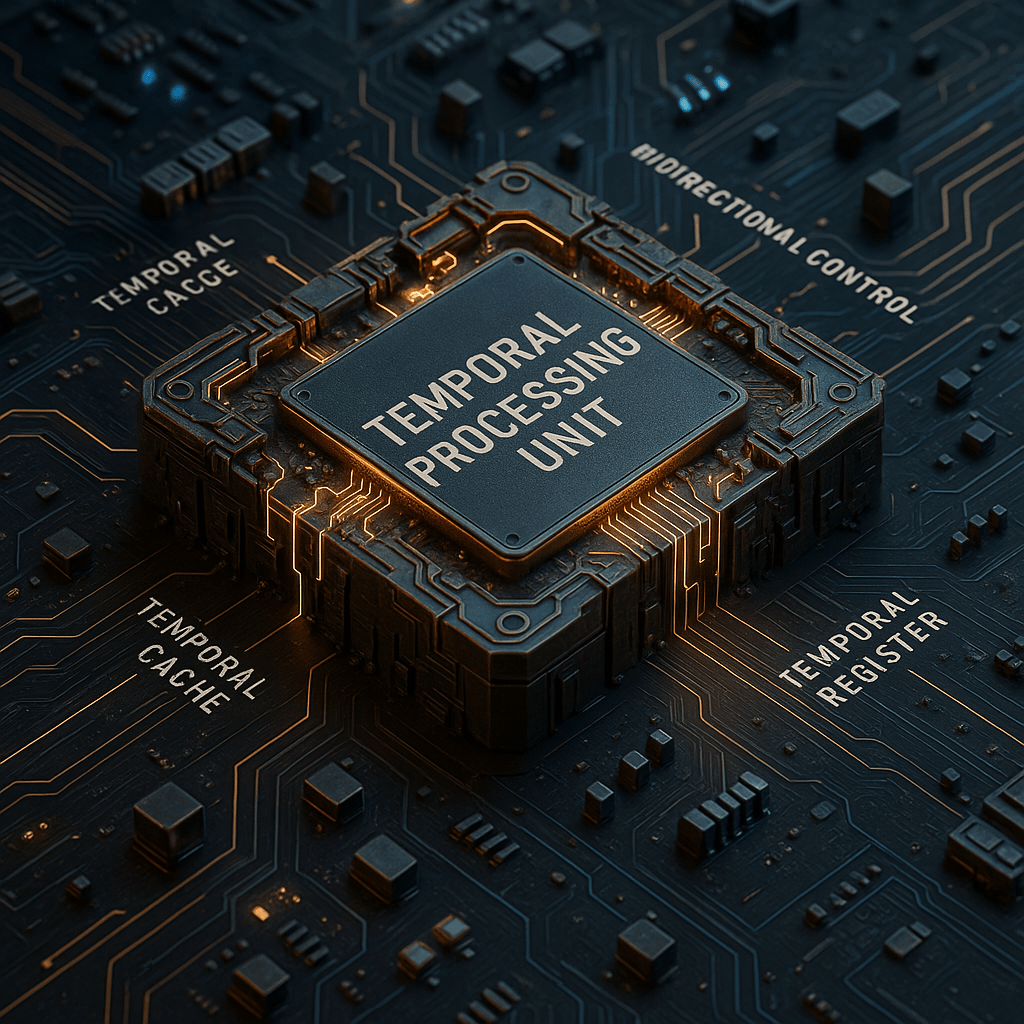

Temporal Processing Unit (TPU)

1.1 Introduction to TDCC Architecture

The Temporal Distortion Computational Core (TDCC) proposes a revolutionary computational model.

Instead of executing operations linearly through time, TDCC enables bidirectional temporal computation — the ability to dynamically process, reverse, checkpoint, and replay operations across a manipulable time axis.

The primary hardware element enabling this is the Temporal Processing Unit (TPU).

| Component | Purpose |

|---|---|

| Temporal Processing Unit (TPU) | Manages time-reversed execution cycles, allowing computational processes to flow both forward and backward through time with complete state fidelity. |

2. Temporal Processing Unit (TPU) Functional Overview

2.1 Core Functionalities of the TPU

The TPU must perform several groundbreaking functions:

2.1.1 Bidirectional Computation Management

Unlike classical CPUs, which execute instructions sequentially (1 → 2 → 3), the TPU enables live reversal (3 → 2 → 1) during runtime without halting or corrupting the computation.

This reversibility must be supported down to the instruction and memory transaction levels, requiring fundamental redefinition of execution pipelines.

2.1.2 Computational Entropy Preservation

Traditional computation is inherently lossy: previous states are overwritten, and irreversible logic gates generate heat through entropy.

In TDCC, computational entropy must be preserved or managed during both forward and reverse operations.

Possible entropy management methods include:

- State Symmetry Mapping: Storing intermediate reversible states in shadow registers.

- Entropy Sinks: Specialized superconducting channels or condensate reservoirs that absorb excess entropy without degrading system stability.

- Instruction Energy Balancing: Hardware may record the energy footprint of operations and reverse it along with logical state during reverse execution.

Without entropy management, reversing computations would lead to non-recoverable data corruption or system destabilization.

2.1.3 Temporal Checkpointing

Checkpoints must not simply snapshot memory — they must freeze the entire computational dynamic state, including:

- Memory contents

- CPU register states

- Thread scheduler queues

- Internal clock drift

- Active thread interaction graphs

Temporal checkpoints would exist as recoverable nodes across a computational timeline, allowing non-linear execution branching or rollback at any moment.

2.1.4 Time-Flow Modulation

The TPU supports dynamic adjustment of computational tempo:

- Forward slow — normal execution.

- Forward fast — accelerated execution with checkpoint skipping.

- Pause — execution halts, preserving entangled states.

- Reverse — stepwise or accelerated reversal across saved checkpoints.

This fluid modulation of the execution timeline must occur with minimal latency to avoid desynchronization between computational threads.

2.1.5 Causal Integrity Enforcement

To prevent paradoxical states when reversing computations, the TPU would actively enforce causal graphs — structures where each computational step is aware of its dependencies.

Hardware must guarantee:

- No reversed operation violates its original dependency chain.

- No backward branch can create orphaned or undefined states.

Causal rollback handlers would be embedded into the TPU pipeline, preventing operations like “reading a memory address before it was originally written.”

2.2 Structural Requirements for the TPU

Building the TPU demands the following engineering fundamentals:

| Requirement | Implementation Approach |

|---|---|

| Non-Destructive Instruction Sets | Each instruction must have a mathematically defined inverse with no loss of information. |

| Reversible Memory Controllers | Memory controllers capable of both traditional R/W and exact reversal without introducing asymmetry or residual data. |

| Entangled Processing Threads | Threads must synchronize their causal histories; interdependent operations across threads must respect temporal reversal together. |

| Temporal Entropy Management | Active cooling, entropy balancing, and quantum error correction layers must maintain physical system coherence during bidirectional flow. |

3. Hypothetical Physical Hardware Requirements

3.1 Hardware Concepts Enabling TDCC

| Hardware Concept | Purpose | Hypothetical Implementation |

|---|---|---|

| Quantum Entanglement Cores (QECs) | Maintain coherent computational state across time jumps. | Qubit clusters engineered to maintain entanglement even through timeline bifurcations. |

| Near-Zero Latency Memory (NZLM) | Eliminate latency barriers during high-speed bidirectional execution. | Photonic or atomic-spin storage arrays with switching times measured in femtoseconds. |

| Reversible Logic Gates | Ensure hardware-level forward and reverse symmetry. | Universal reversible gates (Toffoli, Fredkin, Margolus) composing the full logical instruction set. |

| Entropy Management Systems | Mitigate entropic heat buildup during reversal. | Superconducting entropy absorbers, active quantum refrigeration systems, or dynamic entropy migration. |

| Temporal Field Modulators | Manipulate local time dilation/contraction at the circuit level. | Quantum-controlled decoherence modulation zones altering local computational flow rates. |

| Self-Observing Clock Systems | Maintain synchronization across divergent or converging computational timelines. | Atomic dual-clock arrays measuring elapsed time and predictive time simultaneously, supporting forward/reverse drift correction. |

3.2 Emerging Research Suggesting Feasibility

Current technology areas offering potential stepping stones:

- Superconducting Qubits — critical for maintaining stable entangled states over time (IBM, Google Quantum AI).

- Photonic and Optical Lattice Memory — near-instantaneous data retrieval/storage without electron-based bottlenecks (MIT, Nature Photonics).

- Reversible Computing Architectures — early-stage proof that non-destructive computation is theoretically viable (University of Tokyo, MIT CSAIL).

- Quantum Teleportation Networks — real-time quantum state synchronization between non-local nodes.

While each is promising, none yet fulfill the totality of TDCC requirements, particularly at macro-computational scales.

3.3 Primary Engineering Challenges

| Challenge | Obstacle |

|---|---|

| Energy Costs of Reversibility | Maintaining low-entropy, high-coherence states during bidirectional execution will require significant and continuous energy input. |

| Temporal Synchronization Across Threads | Large-scale entanglement between parallel processes must resist quantum decoherence and timing drift across billions of operations. |

| Instruction Causality Maintenance | Detecting and preventing paradoxical dependencies when reversing instruction flow, especially in multi-threaded or distributed systems. |

4. Consolidated Summary

| Area | Requirement | Impact |

|---|---|---|

| Hardware | Quantum entanglement cores, reversible memory architectures, zero-latency data pathways, entropy mitigation systems | Enables full bidirectional, causally-consistent computational operations with reversible timeline management. |

5. Final Thought: Real-World Implications of TDCC

If realized, TDCC systems would not simply accelerate computation — they would redefine the relationship between programs, memory, time, and causality itself.

Key transformative implications include:

- Time-Reversible Simulations: Scientific modeling (e.g., fluid dynamics, biological systems) could be re-run both forward and backward without state loss, enabling deeper insights.

- Perfect Forensic Computing: Cybersecurity and audit systems could rewind execution history precisely, reconstructing any event or intrusion down to the instruction level.

- Error-Free Debugging: Software could be debugged not only by forward stepping but by rolling back causally to the exact fault origin, with perfect timeline integrity.

- Energy-Efficient Reversible Computing: Long-term, managing computational entropy directly may open new frontiers in low-energy, high-density supercomputing.

Ultimately, TDCC represents the fusion of computation with programmable time control — a leap not simply in speed or capacity, but into an entirely new dimension of control.

If classical computing was the birth of digital logic, TDCC could represent the birth of digital chronology.

https://counter.news/theoretical-design-of-a-temporal-distortion-computational-core-tdcc/